发布日期:2022-05-13

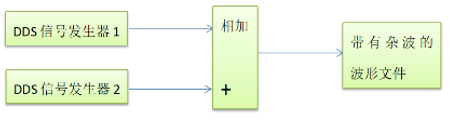

程序介绍:分别使用两个rom输出不同频率,进行相加。

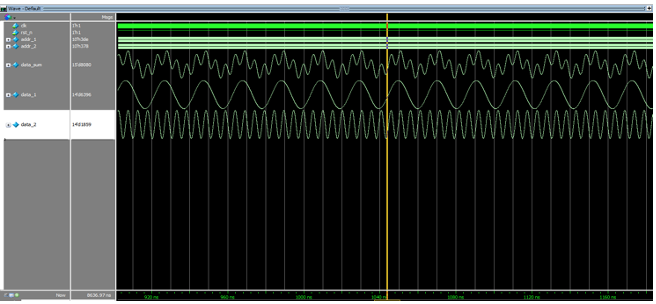

频率计算:使用时钟/采样点=真实频率。

module top (

input wire clk,

input wire rst_n

);

//----------- Registers Declarations

reg [9:0] addr_1;

reg [9:0] addr_2;

reg [14:0] data_sum;

//----------- Wired signal declaration

wire [13:0] data_1;

wire [13:0] data_2;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

begin

addr_1 <= 10d0;

addr_2 <= 10d0;

end

else

begin

addr_1 <= addr_1+10d1; //一个正选波采样点为 1024,输出正选波频50/1024=48.82Khz

addr_2 <= addr_2+10d4; //一个正选波采样点为 256,输出正选波频率 50/256=488Khz

end

end

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

data_sum <= 15d0;

else

data_sum <= data_1 + data_2;

end

rom_1 u_rom_1(

.address (addr_1 ),

.clock (clk ),

.q (data_1 )

);

rom_1 u_rom_2(

.address (addr_2 ),

.clock (clk ),

.q (data_2 )

);

endmodule

仿真结果:data_sum为相加后的结果!

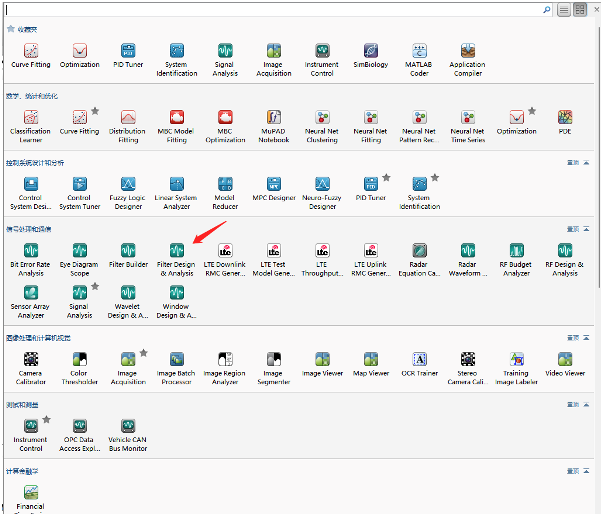

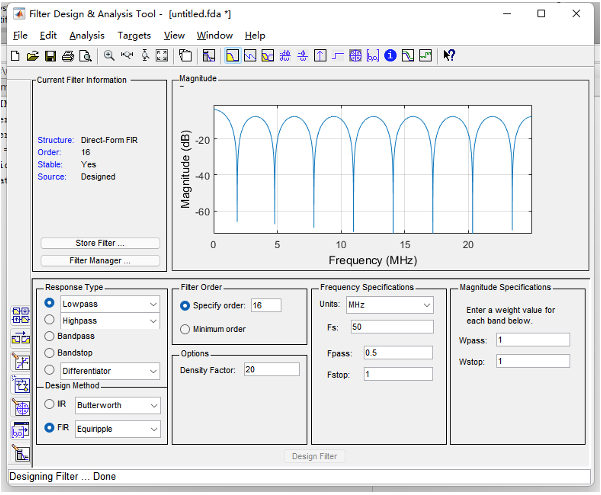

设计一个16阶的低通滤波器

参数选择:选用低通滤波器,使用波纹设计法,阶数自定义了16个(当然阶数越多滤波效果越好),FS的采样频率是50M,通过频率0.5M,截至频率为1M。

Response Type:选择FIR滤波器的类型:低通、高通、带通和带阻等。

Design Method:FIR滤波器设计方法有多种,最常用的是窗函数设计法(Window)、等波纹设计法(Equiripple)和最小二乘法 (Least-Squares)等。其中窗函数设计法在学校课堂中是重点讲解的,提到FIR滤波器肯定会想到hamming、kaiser窗,但是实际应用中却很少使用,因为如果采用窗函数设计法,达到所期望的频率响应,与其它方法相比往往阶数会更多;而且窗函数设计法一般只参照通频带wp、抑制频带ws 和理想增益来设计滤波器,但是实际应用中通频带和抑制带的波纹也是需要考虑的,那在这种情况下,采用等波纹设计法就非常适用了。

Frequency Specification:设置频率响应的参数,包括采样频率Fs、通带频率Fpass和阻带频率Fstop。

Filter Order:设置滤波器的阶数,这个选项直接影响滤波器的性能,阶数越高,性能越好,但是相应在可编程逻辑芯片实现耗用的资源需要增多。在这个设置中提供2个选项:Specify order和Minimum order,Specify order是工程师自己确定滤波器的阶数,Minimum order是让工具自动确定达到期望的频率相应所需要的最小阶数,因此具体选择哪个选项得视实际情况而定了,(这里我选用16阶)。

将配置完成后的数据导出 :

File ---> Export ---> Export ;

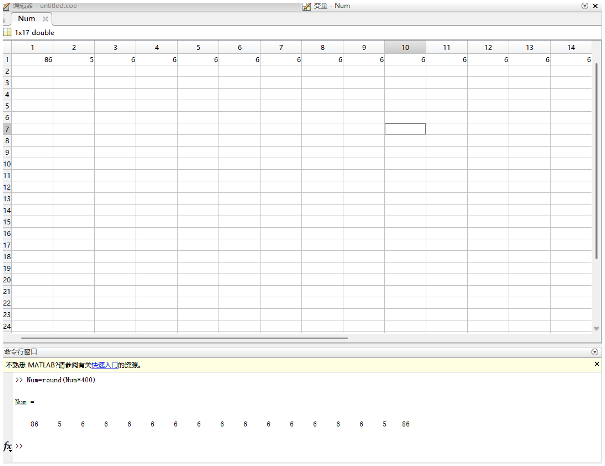

输入 : > Num=round(Num400) 取个整

将下方数据代入到verilog进行乘类加滤波。(无符号)