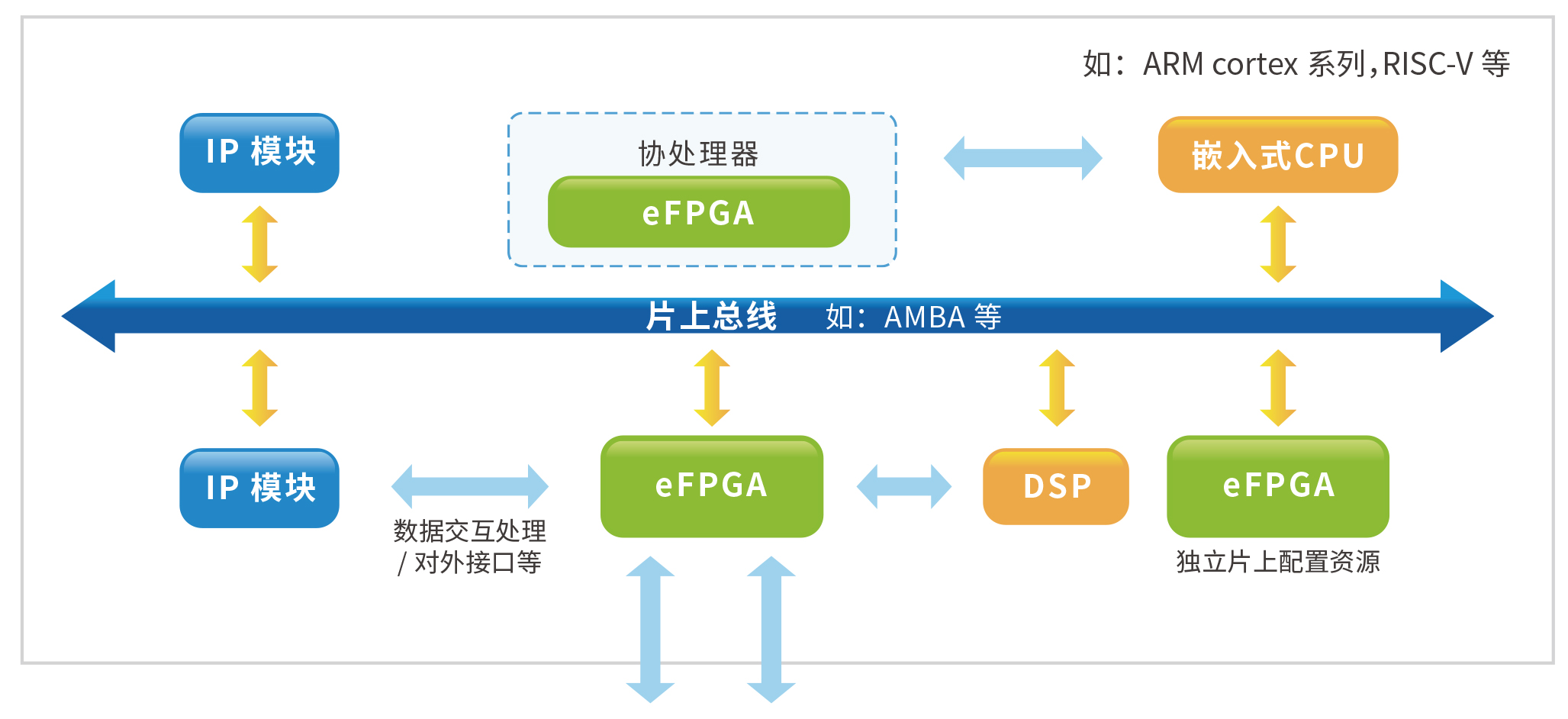

嵌入式可编程电路IP核是一种可重构电路知识产权(IP),由可编程逻辑、可编程互连、可编程块存储器和可编程数字信号处理器等资源组成,该技术可应用于片上系统(SoC),集成电路(ASIC)以及系统级封装(SiP)中,在保持高性能的同时保留一定的灵活性,从而具备软件定义硬件的能力。

● 无I/O模块、面积小、功耗低、传输速度快。

● 片上直接互连,可实现更高带宽。

● 使芯片可兼顾ASIC高速和可编程逻辑芯片灵活性的优点。

● 与国外相比,交付周期更短。

● 本土化迅捷的FAE服务,可以与国内用户紧密配合,协助完成SoC用户应用电路设计需求。

嵌入式可编程电路 IP 核集成应用方式图

| 亿灵犀®6系 | 亿灵犀®9系 | |

| LUT结构 | 4输入查找表结构 | 自适应6输入查找表 |

| 可支持最小规模LUT数量 | 640 | 160 |

| BRAM | 4Kbits Block Memory | 9Kbits Block Memory |

| DSP | 36bits multiplier/18bits accumulator | 54bits multiplier/18bits accumulator |

| 交付方式 | GDSII格式硬核 | |

| EDA软件 | 通过自主EDA设计套件亿灵思(eLinx)完成前期评估流程以及后期从RTL到Bitstream的全流程 | |

已获得市场认可,为用户提供IP授权,成功集成在SoC芯片中得到实际应用。

获得IP SoC China 2019唯一的“国产最具潜力IP设计奖”。

已完成三次硅验证,通过多轮测试验证,功能、性能指标、稳定性均达到设计预期。

基于正向可编程逻辑芯片软硬件设计技术,自主研发可编程逻辑芯片IP Compiler工具,可以针对用户需求,快速定制设计各种嵌入式可编程电路IP核(包括逻辑规模、存储容量、信号处理模块规模等)。