发布日期:2021-08-03

• IP核

IP核称为知识产权核,在集成电路的可重用设计方法学中,指某一方提供的形式为逻辑单元、芯片设计的可重用模组,也就是具有独立功能的电路模块,用户可以使用不同的IP核来进行芯片的设计。模块化设计可以降低整个芯片的开发难度,从而降低芯片设计公司的门槛,缩短开发周期,是芯片设计行业中非常重要的一部分。

• 嵌入式可编程电路IP核

嵌入式可编程电路IP核是一种数字可重构结构的IP核,由可编程逻辑、可编程互连等资源构成,可嵌入到ASIC、SoC、ASSP等专用芯片设计中,可为软件定义芯片提供有效的解决方案。

在结构上,嵌入式可编程电路IP核与可编程逻辑芯片相比,嵌入式可编程电路IP核不包含可编程逻辑芯片中的可编程输入输出单元,只包含可编程逻辑单元、DSP、Memory。同等逻辑密度的嵌入式可编程电路IP核要比可编程逻辑芯片尺寸更小、功耗更低、传输速度更快、带宽更高。

近几年,嵌入式可编程电路IP核的概念已经受到了业界的广泛认可。国外某知名企业凭借嵌入式可编程电路IP核的强劲势头,2017年的营收较2016年增长了700%,2018年IP收入超过5000万美元,这充分说明了嵌入式可编程电路IP核在未来具有巨大的发展空间。

如今,随着人工智能、机器学习等应用场景的快速发展演进,为了应对在高性能、灵活性和上市时间等方面的不同需求,采用嵌入式可编程电路IP核的解决方案将具有非常大的优势,未来嵌入式可编程电路IP核技术势必将在市场上大放异彩。

IP核开发的技术难度和要求很高,一方面IP核自身设计时不能出任何差错,保证其在整个芯片系统中与其他IP核或模块的完美配合,另一方面要求工艺节点和技术性能指标能够满足各应用行业需求。嵌入式可编程电路IP核作为一种IP核,其对设计人员的技术要求和对设计公司的综合实力要求都有着很高的挑战。

嵌入式可编程电路IP核厂家在设计过程中,要根据目标应用场景的实际需要,对其架构、尺寸、性能和制造工艺节点进行定制化研制。同时在研制过程中,流片金属层数量、管理时钟域边界、协调不同电源管理方案和降低用户使用难度的易用性设计等也是嵌入式可编程电路IP核厂家面临的技术挑战。此外,在研发过程中,除了对IP核进行设计,还需要对其配套的EDA工具软件进行定制化开发,帮助用户进行快速开发与部署。

亿海微具有国内顶级的研发团队和成熟的FAE队伍,在嵌入式可编程电路IP核和EDA软件领域具有10余年的技术积累和丰富的应用支持经验。公司现有成熟的基于40nm工艺制程的亿灵犀系列嵌入式可编程电路IP核,可按用户需求进行定制设计,可以提供对外设计服务。

5.1 硬件架构

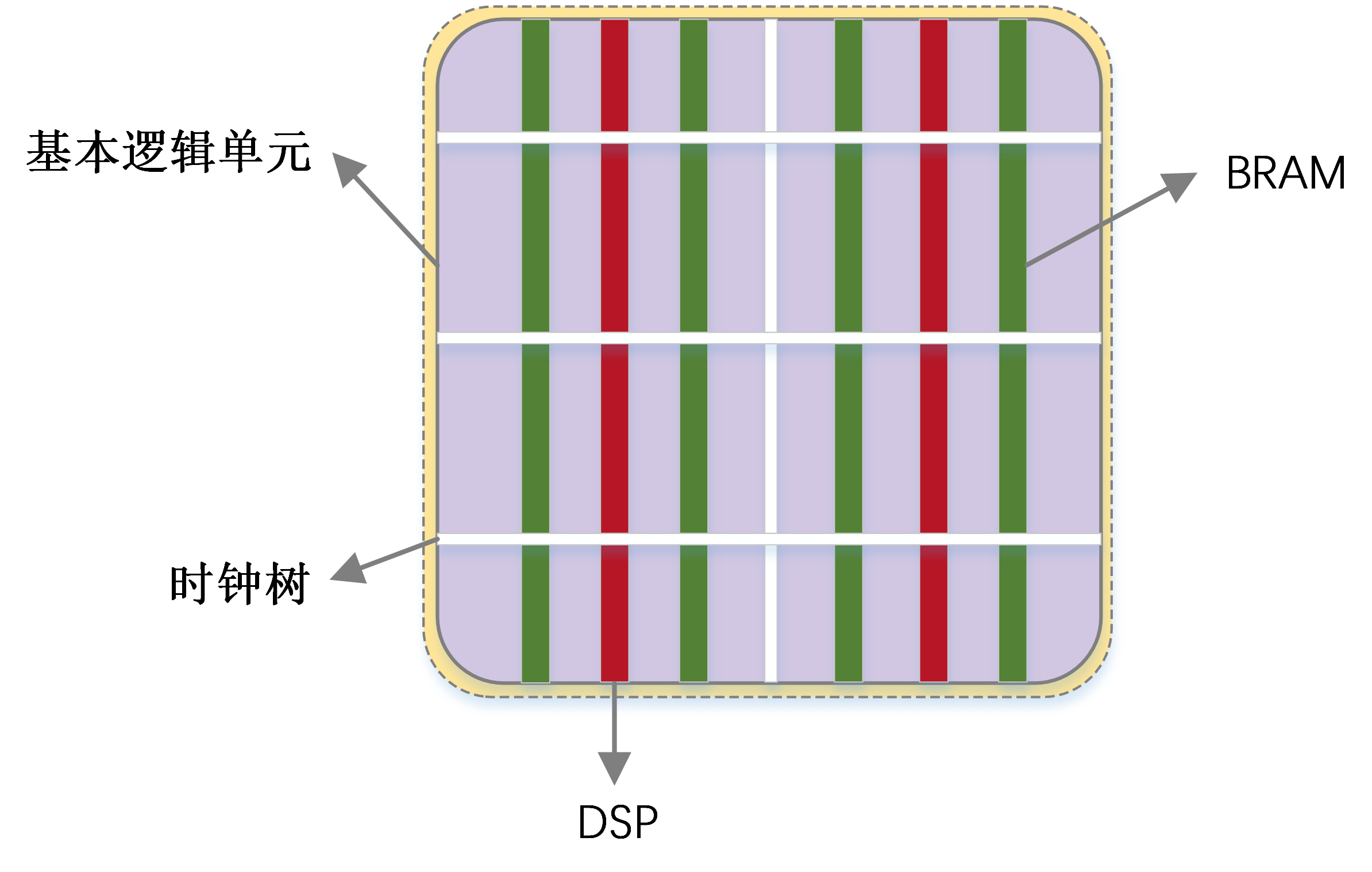

亿海微自主研发的国产嵌入式可编程电路IP核的硬件架构如下图所示:

用户可以根据使用需求自定义资源类型、数量、物理尺寸和形状。同时,团队也为用户提供配套的自主研发的IP核评估软件,便于用户进行芯片集成设计的前期评估工作。

5.2 开发流程

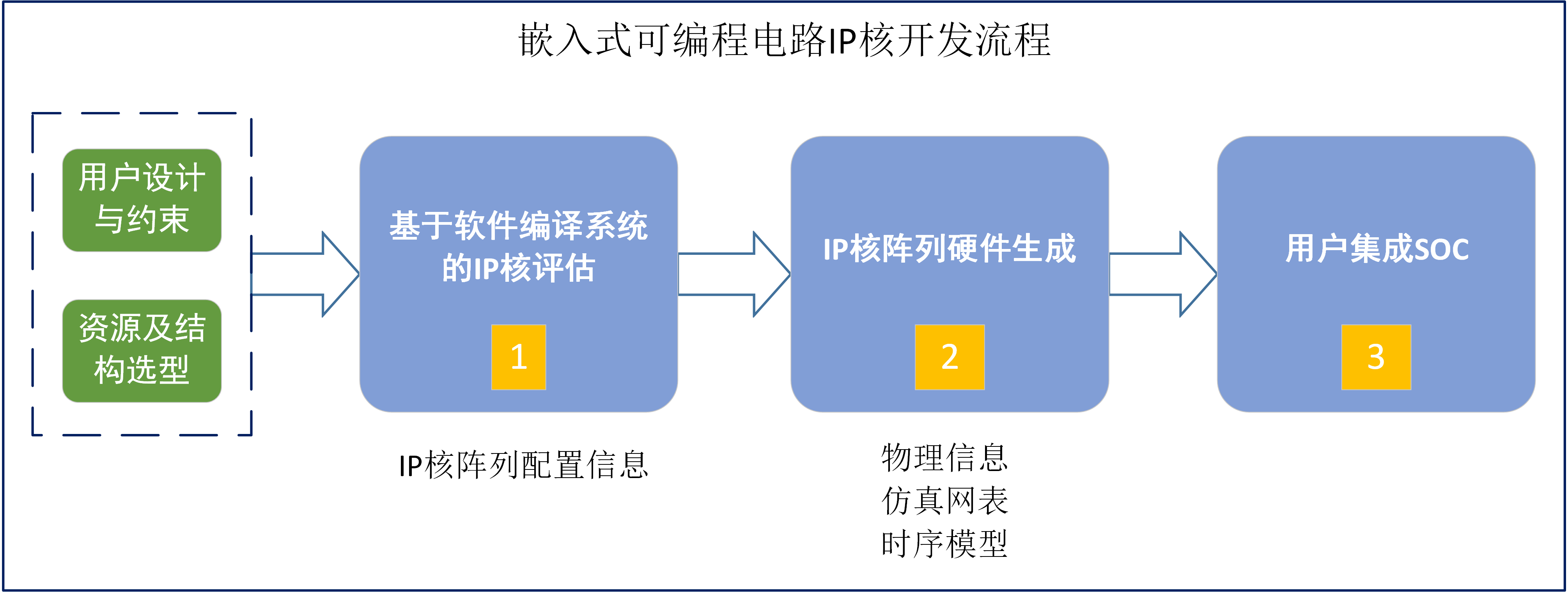

亿海微嵌入式可编程电路IP核的开发流程如下图所示:

用户综合考虑用户设计约束和资源结构,进行资源评估,生成IP核阵列配置信息,然后根据阵列配置信息提交团队,生成IP核硬件电路结构,并产生嵌入式可编程电路IP核的物理模型、功能模型和时序模型,以满足用户进行进一步的芯片集成设计。下图所示为亿海微某工艺节点下的嵌入式可编程电路IP核的测试芯片的版图:

5.3 技术优势

• 亿海微是目前境内唯一一家提供国产先进工艺嵌入式可编程电路IP核设计并已经交付客户使用的公司,目前已经完成多次硅技术验证,功能、性能指标和稳定性均已达到了预期效果;

• 相较于同等资源的可编程逻辑芯片,嵌入式可编程电路IP核在尺寸、延时、功耗、带宽等方面都具有更强的优势。研发团队可针对不同的应用场景需要进行灵活便捷的定制化设计,生成不同资源、版图物理尺寸和形状的嵌入式IP核;

• 亿海微具有成熟的软硬件编译技术,确定应用需求规格条件后,产品交付周期为2~3个月,能够满足SoC用户应用电路设计需求;

• 获得IP SOC China 2019年度唯一的“国产最具有潜力IP设计奖”;

• 2019年10月,荣获“国科大杯”双创大赛新一代信息技术类决赛一等奖。

|

|

IP SOC China 2019 唯一的“国产最具潜力IP设计奖” | “国科大杯”双创大赛 新一代信息技术类决赛一等奖 |