发布日期:2023-12-22

一、技术概述

FPGA实现除法运算是一个比较复杂的过程,因为硬件逻辑与软件程序的区别。如果其中一个操作数为常数,可以通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成。因此,FPGA实现除法运算并不是一个“/”号可以解决的。总体来说,在FPGA中做基本的数学运算没什么难度,即使是指数、对数、开根号之类的复杂运算也有浮点IP Core的支持。如果需要实现复杂算法,可以采用HLS方式开发,仅用于算法验证。

二、技术应用场景

FPGA除法器技术主要应用于数字信号处理、通信系统、图像处理、高速计算机、测量仪器等领域。在这些领域中,需要对数据进行除法运算,而FPGA除法器可以提供高速、低功耗、低成本的除法运算解决方案。例如,在通信系统中,需要对信号进行解调、解码等操作,这些操作中需要进行除法运算,而FPGA除法器可以提供高效的解决方案。在图像处理中,需要对图像进行缩放、旋转等操作,这些操作中也需要进行除法运算,而FPGA除法器可以提供高速的图像处理能力。此外,FPGA除法器还可以应用于各种算法中,例如卷积神经网络、快速傅里叶变换等。

三、优势和不足

优势:

1)FPGA除法器可以实现高精度的除法运算,比如非恢复余数除法器可以实现更高的除法精度。

2)FPGA除法器可以在数字电路中快速执行除法运算,比软件实现更快速。

3)FPGA除法器可以根据需要进行定制化设计,满足不同应用场景的需求。

不足:

1)FPGA除法器的设计和实现比较复杂,需要专业的知识和技能。

2)FPGA除法器的资源占用比较大,需要占用较多的FPGA资源。

3)FPGA除法器的功耗比较高,需要考虑功耗管理和优化。

四、技术原理和实现方法

FPGA除法器是一种基于FPGA芯片实现的除法器,其原理是通过将被除数不断减去除数,直到被除数小于除数为止,每次减法操作都会使商数加1,最终被除数减去的结果就是余数。

五、技术实现案例和效果展示

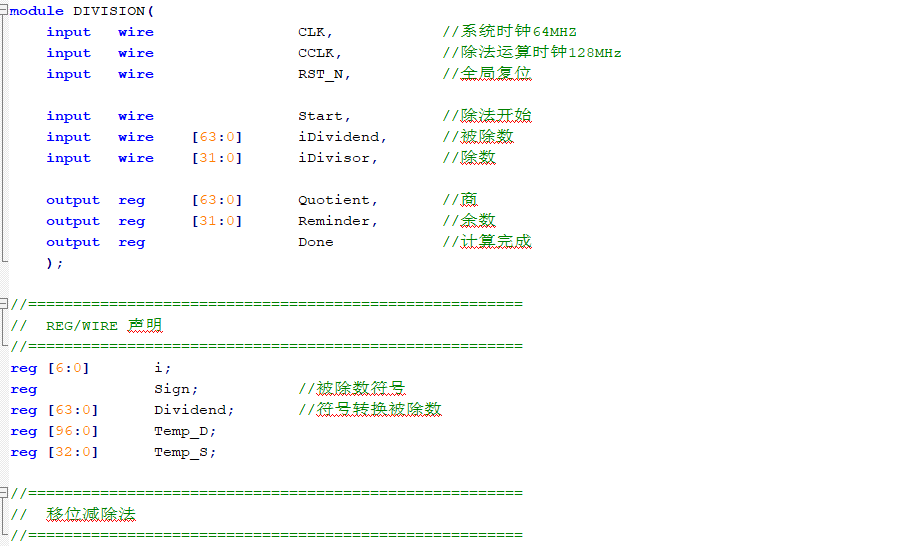

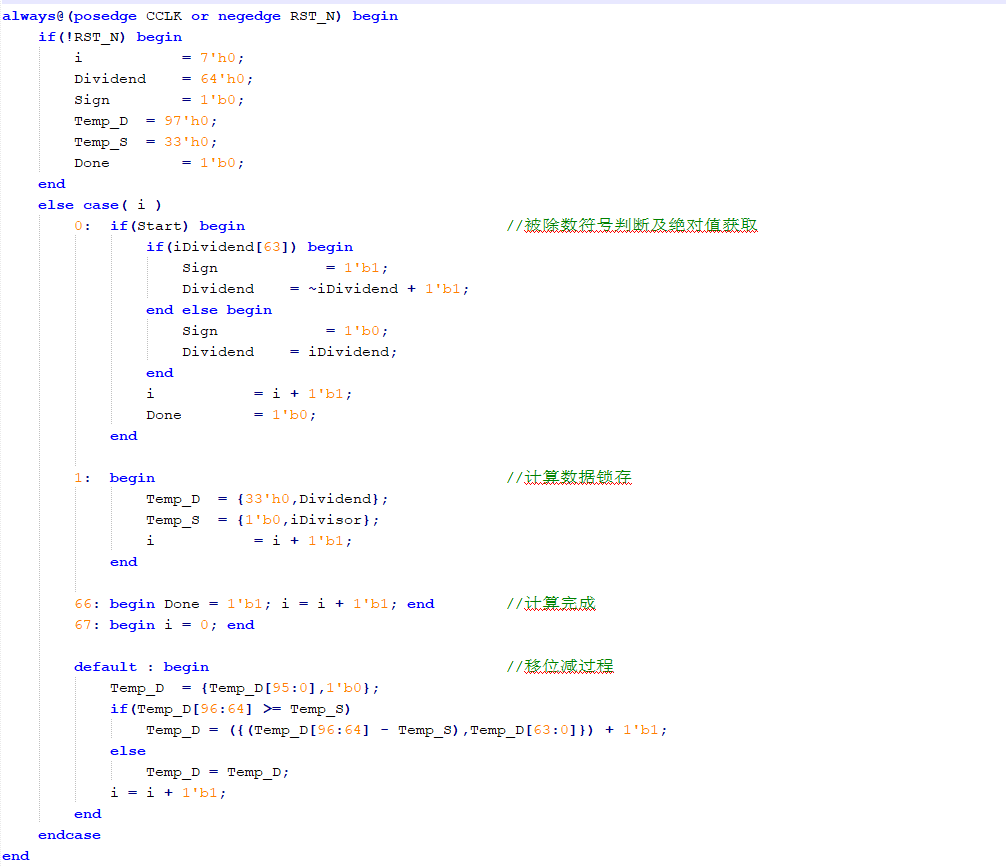

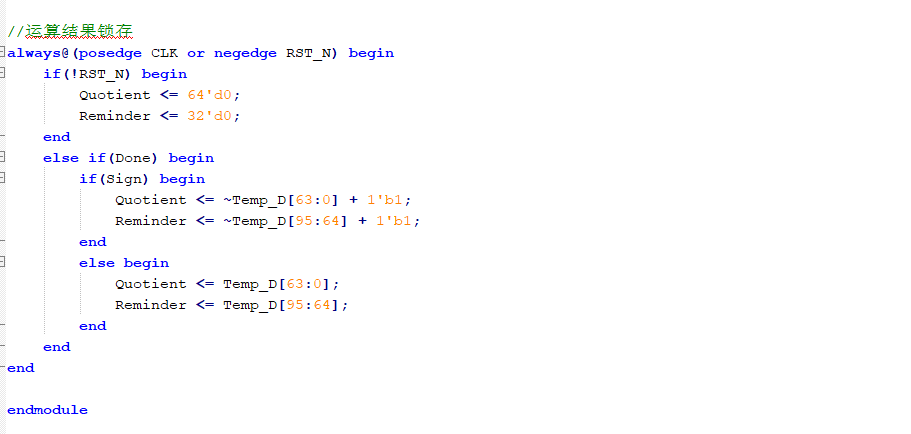

实现方法一:开发一套除法器算法。

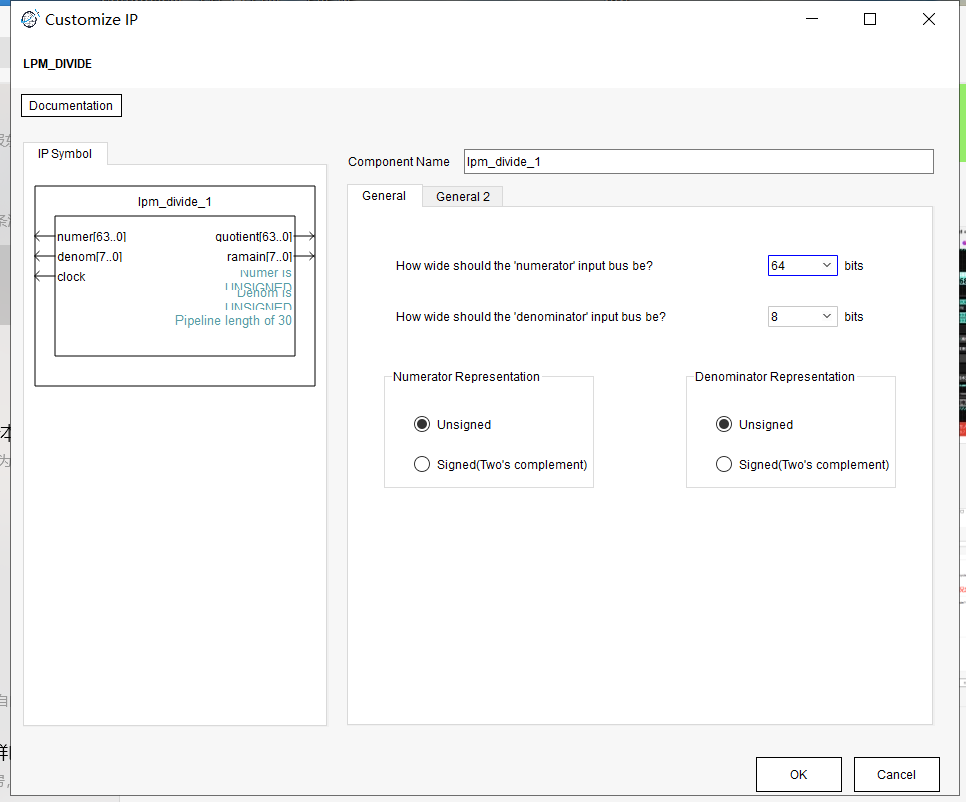

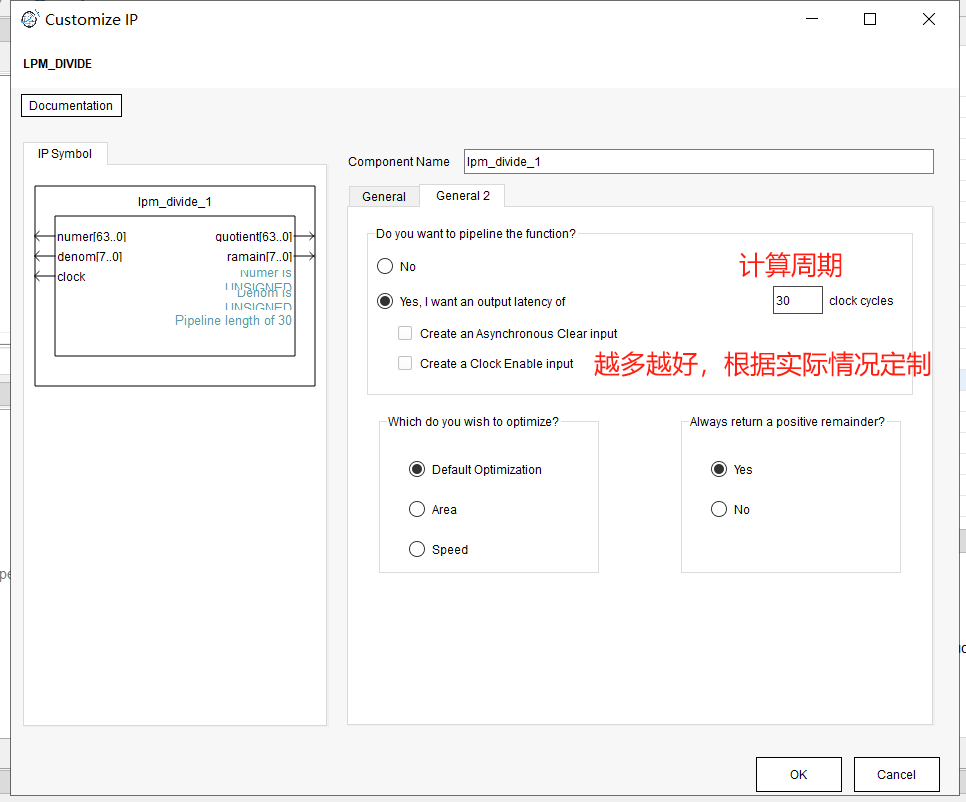

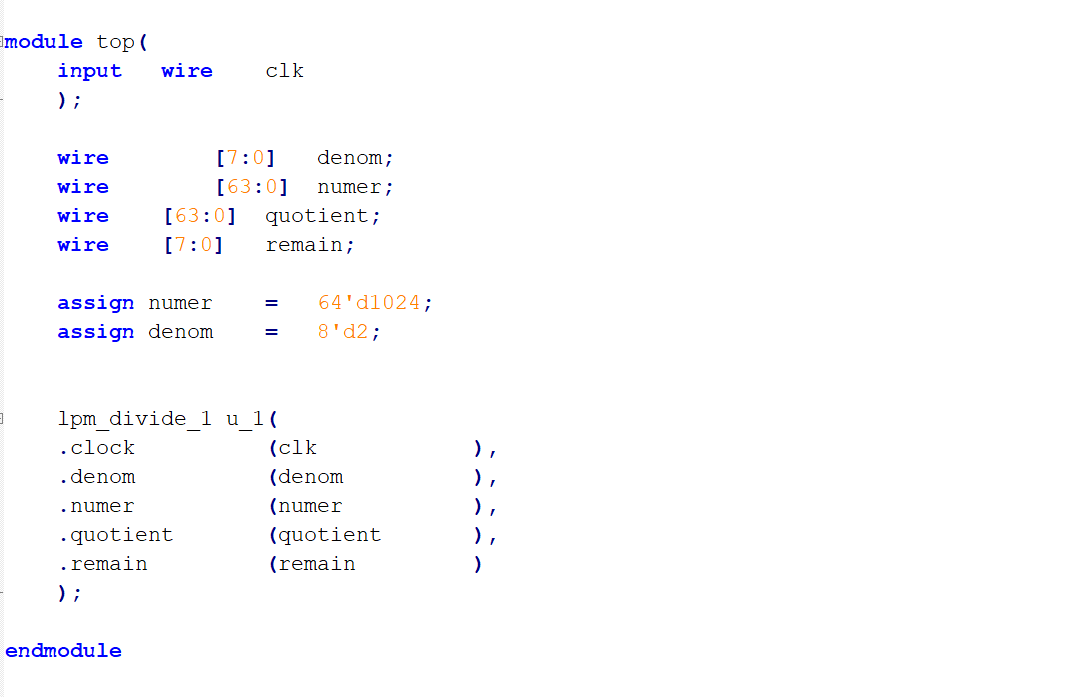

实现方式二:使用IP核操作。

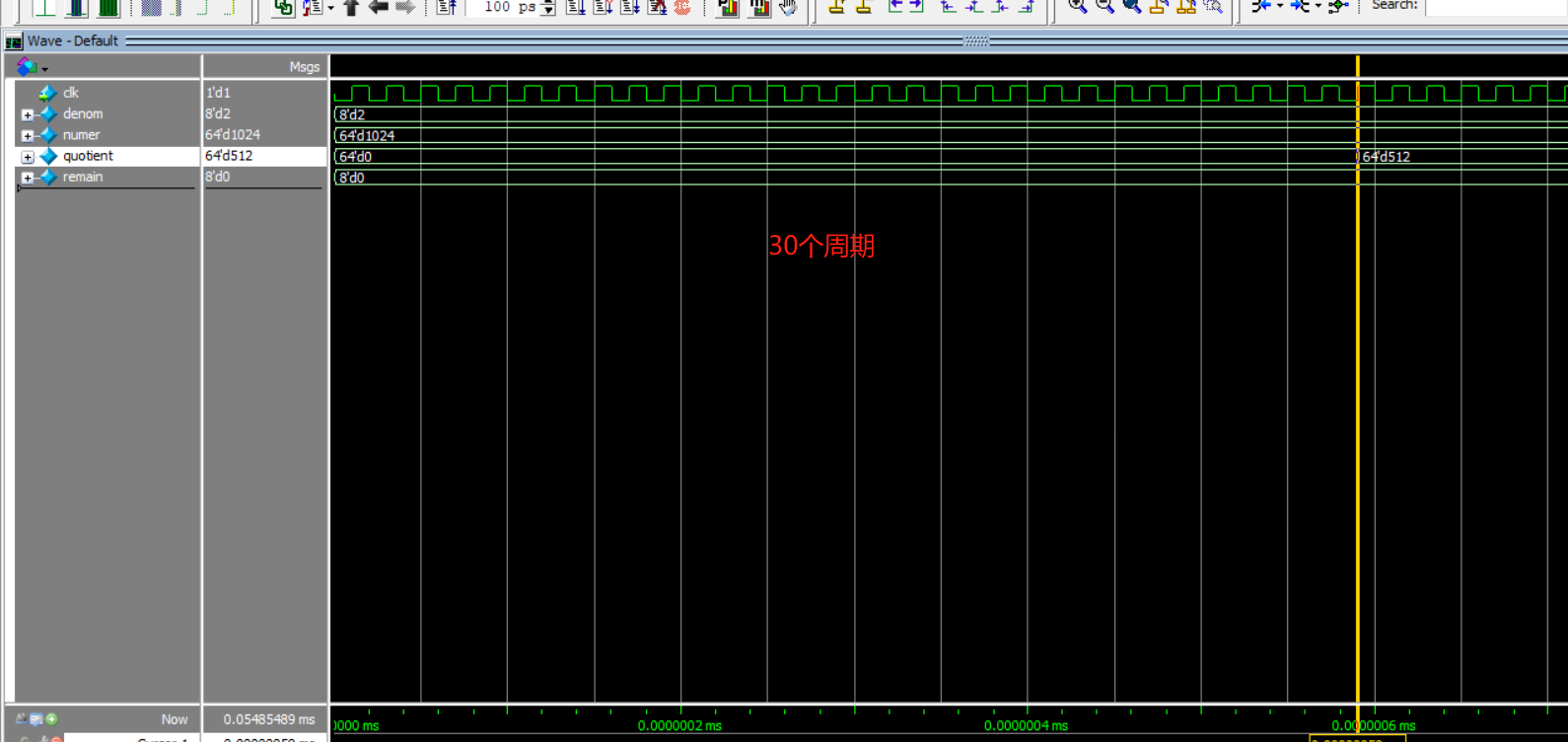

仿真结果:

六、总结

使用IP核可以减少设计人员的工作量,因为IP核已经经过验证和测试,可以直接使用,而不需要重新设计和验证。提高性能:使用IP核可以提高设计的性能,因为IP核是专门为特定的任务设计的,可以充分利用FPGA的硬件资源,从而提高性能。降低功耗:使用IP核可以降低功耗,因为IP核是经过优化的,可以使用更少的资源来完成任务,从而降低功耗。提高可靠性:使用IP核可以提高设计的可靠性,因为IP核已经经过验证和测试,可以保证其正确性和稳定性。

引用

“用于加密应用的基于 FPGA 的高速分频器”,IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2015 年。

“基于FPGA的高速分频器的设计与实现”,《国际可重构计算杂志》,2016年。

“用于数字信号处理应用的基于 FPGA 的高性能分频器”,IEEE Transactions on Circuits and Systems II:Express Briefs,2017 年。

“使用Verilog HDL设计和实现基于FPGA的高速分频器”,国际电子与通信工程与技术杂志,2018年。

“一种用于高速应用的新型基于FPGA的分频器”,《信号处理系统学报》,2019年。

https://download.csdn.net/download/XingouChen/13216328