发布日期:2023-09-28

一、引言

FPGA(可编程逻辑门阵列)是一种可在硬件级别上重新配置的集成电路,它具有灵活性和可重构性,使其成为处理各种应用的理想选择,包括数字信号处理、图像处理、通信、嵌入式系统等。在FPGA中,乘法器是一种重要的硬件资源。乘法器用于执行乘法运算,可以在数字信号处理、滤波、图像处理、嵌入式系统等领域中发挥关键作用。传统的乘法运算通常采用基于加法和移位的算法,但这些方法可能需要较长的计算时间,并且在某些应用中效率较低。为了提高计算效率,FPGA芯片通常会集成专门的乘法器资源。FPGA中的乘法器通常是基于二进制乘法算法实现的。这些乘法器可以支持不同大小的操作数,例如8位、16位、32位或更大。乘法器通常具有高速、低功耗和高精度的特点,能够在短时间内完成大量复杂的乘法运算。乘法器的设计和优化是FPGA开发中的重要课题之一。设计者需要考虑乘法器的延迟、功耗、面积占用和精度等因素,以满足特定应用的需求。同时,还可以通过并行计算、流水线技术和优化算法等方法来提高乘法器的性能和效率。

二、技术概述

在电路中,乘法器是一种用于执行乘法运算的重要组件。它能够将两个输入数相乘,并输出它们的乘积。乘法器在数字信号处理、通信系统、图像处理等领域都有广泛的应用。乘法器的基本原理是基于二进制乘法算法。在二进制乘法中,每个位的乘积可以通过将一个数乘以另一个数的每一位,并将这些部分乘积相加来得到。例如,对于两个4位的二进制数A和B,其乘积可以通过计算A的每一位与B的每一位的乘积,并将这些部分乘积相加得到。乘法器通常采用布斯-加法器(Booths algorithm)或Wallace树(Wallace tree)等算法来实现高效的乘法运算。这些算法利用了二进制数的特性,通过位移、加法和累加等操作来计算乘积。

FPGA芯片中的乘法器是一种硬件资源,用于执行乘法运算,它是通过组合逻辑电路的方式来实现的。FPGA中的乘法器基本原理是基于二进制乘法算法,对于两个n位的二进制数A和B,乘法器会将A的每一位与B的每一位相乘,并将这些部分乘积相加得到最终结果。FPGA中的乘法器通常采用了布斯-加法器(Booths algorithm)或Wallace树(Wallace tree)等高效的算法来实现。这些算法可以减少部分乘积的数量,从而提高计算效率。布斯-加法器是一种基于移位和加法操作来计算乘积的方法,它通过将乘法运算转化为一系列的加法和移位操作,从而实现高速的乘法计算。布斯-加法器通常采用串行或并行的方式来计算乘法结果。Wallace树是一种并行计算的乘法器实现方法,它通过将乘法运算分解为多个部分乘积的累加,从而实现更高的计算速度。Wallace树利用了并行计算的特性,可以同时计算多个部分乘积,提高乘法器的性能。除了布斯-加法器和Wallace树,FPGA中的乘法器还可以采用其他的优化技术和算法来提高计算效率和资源利用率,例如,可以使用部分乘积树、树型累加器等。

三、具体步骤或方法

1、二进制数表示:了解二进制数的表示方法,包括正数、负数和小数的表示方式。

2、二进制加法和移位:理解二进制数的加法运算和移位操作,这是乘法器实现中常用的基本操作。

3、布斯-加法器:布斯-加法器是一种优化的乘法器实现方法,通过减少乘法器中的部分乘积数量,从而提高计算效率。

4、Wallace树:Wallace树是一种并行计算的乘法器实现方法,通过将乘法运算分解为多个部分乘积的累加来提高计算速度。

5、乘法器的延迟和面积:了解乘法器的延迟(计算时间)和面积(硬件资源占用)之间的权衡关系,以及如何进行设计和优化。

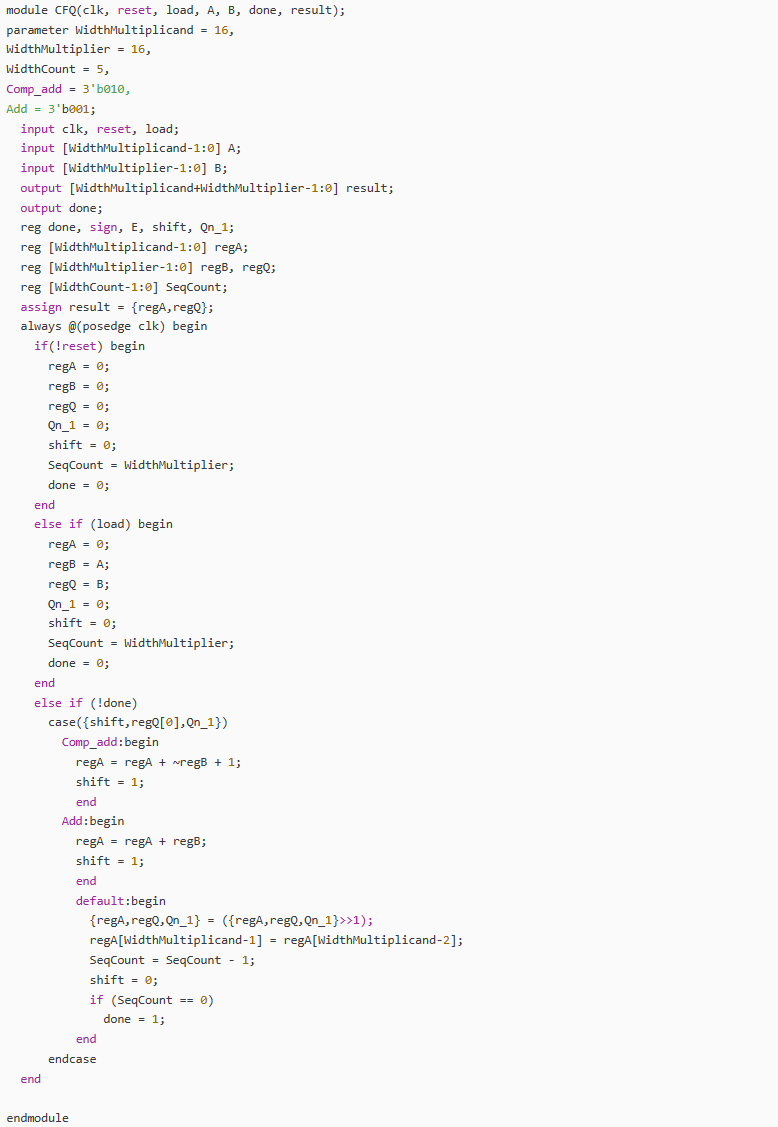

使用Verilog编写的布斯-乘法器的示例代码:

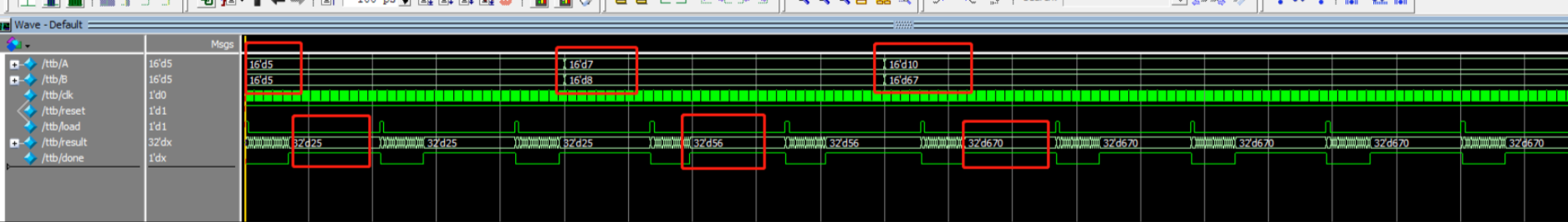

四、实验结果

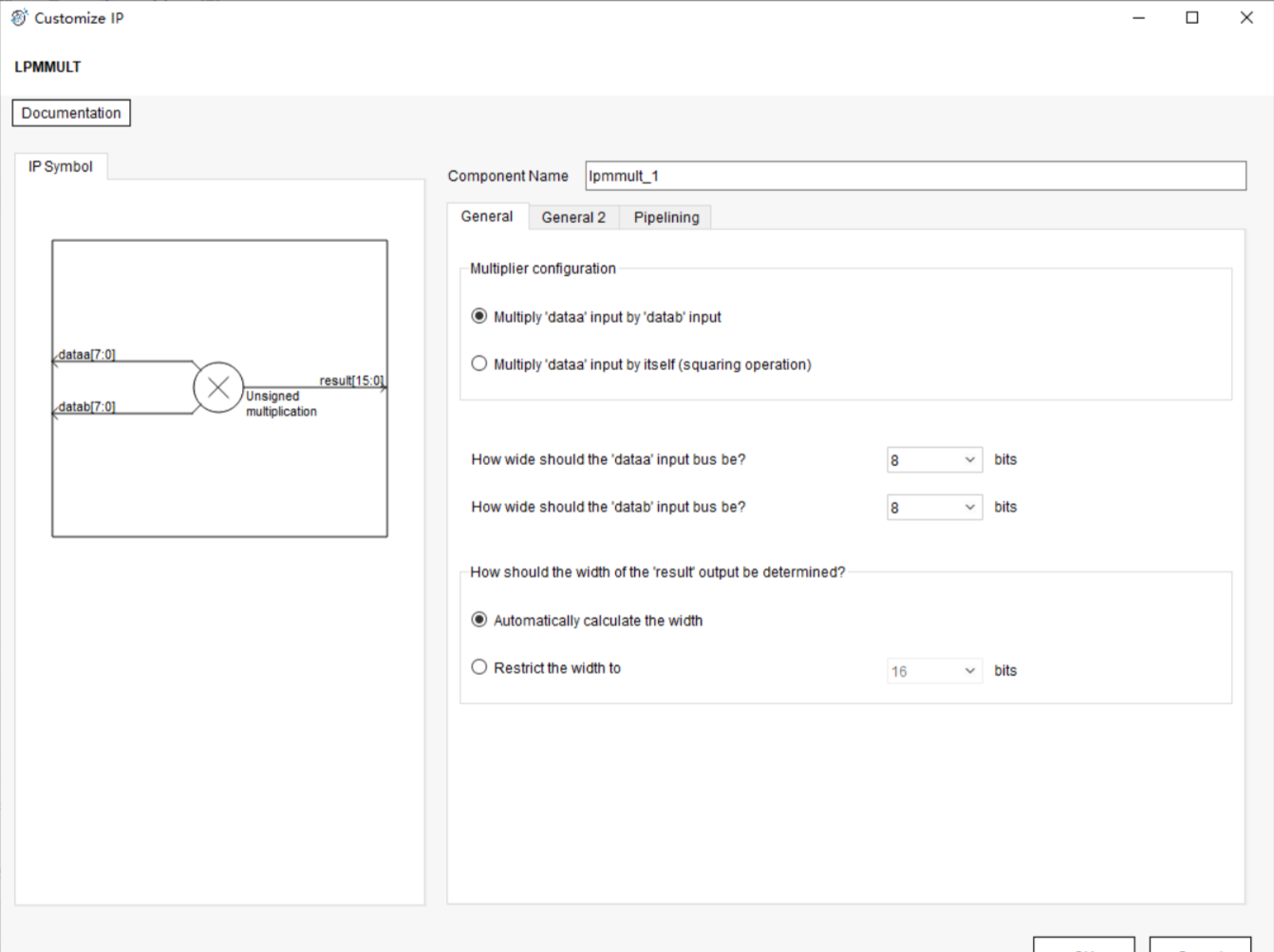

五、使用eLinx工具开发

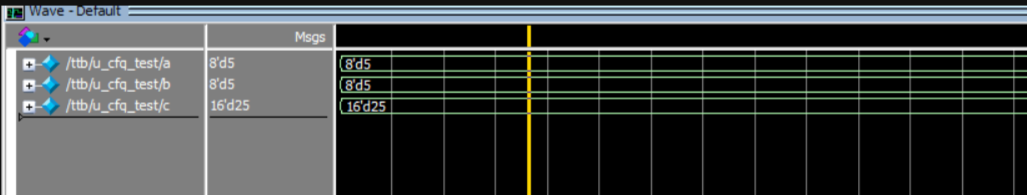

六、实验结果

七、结论

1、确定乘法器的位宽:根据应用需求,确定乘法器的输入和输出位宽,确保适当的位宽可以处理所需的数值范围和精度。

2、选择适当的乘法器结构:根据应用需求和资源限制,选择合适的乘法器结构。常见的结构包括布斯-加法器、Wallace树、Dadda树等。不同的结构具有不同的性能和资源开销,因此需要进行权衡和选择。

3、优化资源利用:FPGA资源有限,因此在设计乘法器时需要考虑资源利用的优化。例如,可以使用乘法器硬件资源共享技术,减少重复使用的硬件单元。

4、考虑时钟和延迟:在设计乘法器时,需要考虑时钟频率和延迟。乘法器的延迟可能会影响整个系统的性能,因此,需要合理设置时钟频率,并进行时序分析以确保正确的操作和稳定性。

5、进行仿真和验证:在将乘法器部署到FPGA之前,进行全面的仿真和验证是非常重要的,通过仿真,可以验证乘法器的功能正确性,并进行性能评估,验证还可以帮助发现和解决潜在的问题和错误。

6、进行资源和功耗优化:对于FPGA设计,资源和功耗优化是关键考虑因素。通过使用合适的优化技术和工具,可以减少乘法器的资源占用和功耗消耗,从而提高设计的效率和性能。

7、考虑设计复杂度和可扩展性:乘法器的设计复杂度随着位宽的增加而增加。因此,在设计乘法器时,需要平衡设计复杂度和可扩展性。合理划分模块,并考虑模块化设计和重用性,以便将来的扩展和修改更加方便。

8、注意时序约束:在FPGA设计中,时序约束是确保正确操作的关键。在设计乘法器时,需要正确设置时序约束,并进行时序分析和优化,以确保信号传输和计算正确。

参考文献

verilog的布斯乘法器资源-CSDN文库 ----- 特别感谢贡献软核代码

1."FPGA Prototyping by Verilog Examples: Xilinx Spartan-3 Version" by Pong P. Chu - 这本书介绍了基于Xilinx Spartan-3 FPGA的Verilog语言和FPGA设计技术。其中包含了有关乘法器设计的章节,并提供了实际的例子和案例分析。

2."Digital Design and Computer Architecture" by David Harris, Sarah Harris - 这本书是关于数字设计和计算机体系结构的综合性教材。其中涵盖了FPGA设计和乘法器的基本原理与实践。

3."FPGAs: Instant Access" by Clive Maxfield - 这本书提供了对FPGA设计和开发的快速入门指南。其中包含了有关乘法器设计和优化的简洁介绍,适合初学者快速了解。

4."FPGA-d Implementation of Signal Processing Systems" by Roger Woods, John McAllister, Gaye Lightbody, Ying Yi - 这本书深入介绍了FPGA在信号处理系统中的应用。其中包括乘法器设计和优化的内容,并提供了实际的案例和应用示例。

5."Digital System Design with FPGA: Implementation Using Verilog and VHDL" by Cem Unsalan, Bora Tar - 这本书涵盖了FPGA设计的基础知识和实践技巧。其中包含有关乘法器设计和优化的章节,适合初学者和有一定经验的设计工程师阅读。